RGBLED

简介

-

像素点, 分辨率: 略

-

尺寸不变, 分辨率越高显示的效果越好

-

PPI: 屏幕对角线的像素点数目, 除以对角线的英寸数字

-

像素格式: 对RGB颜色进行量化, 每一种使用8bit进行表示描述颜色, 现在也流行10bit, HDR10支持HDR效果的10bit面板, 在RGB888基础上再加上ALPHA通道也就是透明通道ARGB888

-

屏幕接口, RGB格式的屏幕一般为RGB接口屏

接口有MIPI, LVDS, MCU, RGB接口

6ULL支持这些接口

屏幕的ID: 使用不同的ID识别不同的屏幕, 在RGB的R7G7B7上焊接不同的上拉下拉电阻实现不同的ID

正点原子的底板使用了三个模拟开关, 防止影响启动(启动使用的引脚就是这几个LED屏幕的引脚)

时间参数

水平

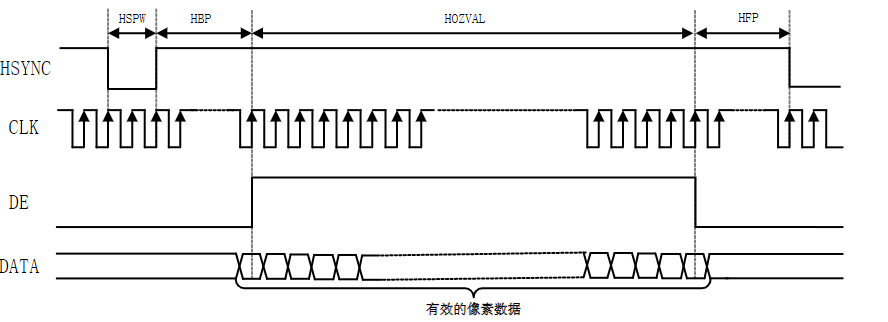

HSYNC是水平同步信号,也叫做行同步信号,当产生此信号的话就表示开始显示新的一行了, 出现的时候表示新的一行开始显示

显示的时序图

- HSYNS信号表示一行的开始, 维持的时间为HSPW 20

- 完成之后需要一段时间的延时, 叫做HBP 240

- 之后就是显示1024个像素数据, 也就是1024个时钟 1024

- 一行结束之后HFP时间等待下一行有效 160

垂直

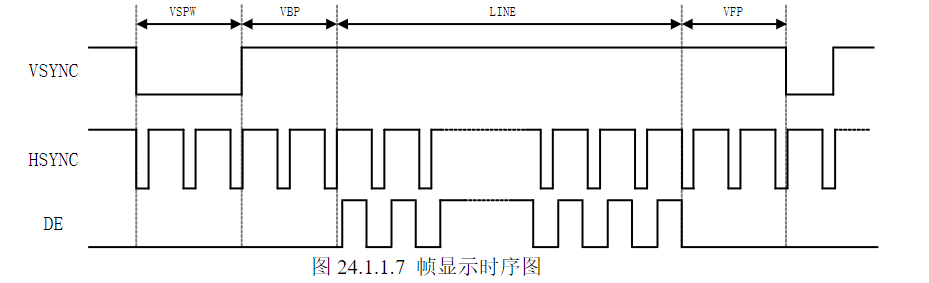

VSYNC信号是垂直同步信号,也叫做帧同步信号,当产生此信号的话就表示开始显示新的一帧图像了

-

VSPW:有些地方也叫做

tvp,是VSYNC信号宽度,也就是VSYNC信号持续时间,单位为1行的时间, 这个设置为三行的时间 -

VBP:有些地方叫做

tvb,术语叫做帧同步信号后肩,单位为1行的时间。这里为20 -

LINE:有些地方叫做

tvd,显示一帧有效数据所需的时间,假如屏幕分辨率为1024*600,那么LINE就是600行的时间 -

VFP:所有行显示完成之后, 有些地方叫做

tvf,术语叫做帧同步信号前肩,单位为1行的时间 12

总时间= (VSPW+VBP+LINE+VFP) * (HSPW + HBP + HOZVAL + HFP)= 853440

那么显示60帧就是:853440*60=51206400≈51.2M,所以像素时钟就是51.2MHz。

引脚

LCD_CLK引脚输出时钟

LCD_HSYNC:

LCD_HSYMN:

LCD_ENABLE: DE信号, 有效的时候显示屏幕的数据

显存

显示存储空间, , 采用ARGB888, 一个像素是四字节, 必须存储起来, 一帧大概是2.5M内存留给显示使用

实现

手册34章

使用DOTCLK接口也就是使用上面列出来的四种接口

寄存器

LCDIF_CTRLn: 通用控制, bit0必须为1, 开始传输数据, bit1设置数据24位设置为0, bit5设置工作在主机模式下, bit8-9输入的数据格式, 设置为3为24位, bit10-11数据传输宽度24位为3, bit12-13数据交换顺序, 设置为0, bit14-15输入交换0, bit17 DOTCLK模式为1, bit19根据模式为1, bit31设置为0不复位

LCDIF_CTRL1n: bit16-19设置格式为24位ARGB 7

LCDIF_TRANSFER_COUNT: bit0-15LCD屏幕水平像素, 16-31垂直像素

LCDIF_VDCTRL0n: 设置性质的性质, bit0-17位VSPW, bit20

vsync信号的单位设置为1行为单位, bit21设置为1, 周期的单位, bit24,25,26,27设置ENABLE系编号0低电平, DOTCLK时钟信号0上升沿有效, HSYNC, VSYNC极性设置0低电平有效, bit28ENABLE信号使能为1, bit29VSYNC输出, 设置为0

LCDIF_VDCTRL1, VSYNC周期长度

LCDIF_VDCTRL2: 0-17HSINC信号长度, 18-31HSYNC信号宽度

hspw

LCDIF_VDCTRL3: bit0-15$vbp+vspw$, bit16-27: $hbp+hspw$

LCDIF_VDCTRL4: bit0-17每一行像素点1024, bit18 为1

LCDIF_CUR_BUF:缓存地址

LCDIF_NEXT_BUF: 下一帧数据地址, 设置为一样的简单处理

IO初始化

时钟设置

时钟配置

LCD需要一个时钟, 这个时钟是CLK发送给RGBLED的大约为51.2MHz, LCDIF1_CLK_ROOT, 设置PLL5也就是videoPLL为时钟源, 有两个分频器

\(PLL5_CLK = OSC24M * (loopDivider + (denominator / numerator)) / postDivider\)

不使用分数进行配置

CCM_ANALOG_PLL_VIDEOn[DIV_SELECT]bit0-6寄存器, 可以选择27-24, bit20-19设置分频

CCM_ANALOG_MISC2n[VIDEO_DIV]另一个分频寄存器bit30-31为0

CCM_ANALOG_PLL_VIDEO_NUM分子寄存器设置为0

CCM_ANALOG_PLL_VIDEO_DENOM分母

CSCDR2[LCDIF1_PRE_CLK_SEL]nit17-15, 选择时钟源 , 设置为2选择PLL5, bit14-12位分频

CCM_CBCMR, bit23-25设施另一次分频

CCM_CSCDR2, bit9-11再次选择时钟, 设置为0

编写

初始化之前读取屏幕的ID, 使用其他的屏幕不需要