主频时钟配置

初始化默认为396M, 最高792M

时钟来源

时钟

晶振1, 32.768kHz, 供给给RTC实时时钟使用

晶振2, 在T16和T17上有一个24MHz的晶振

时钟的构成

手册18章

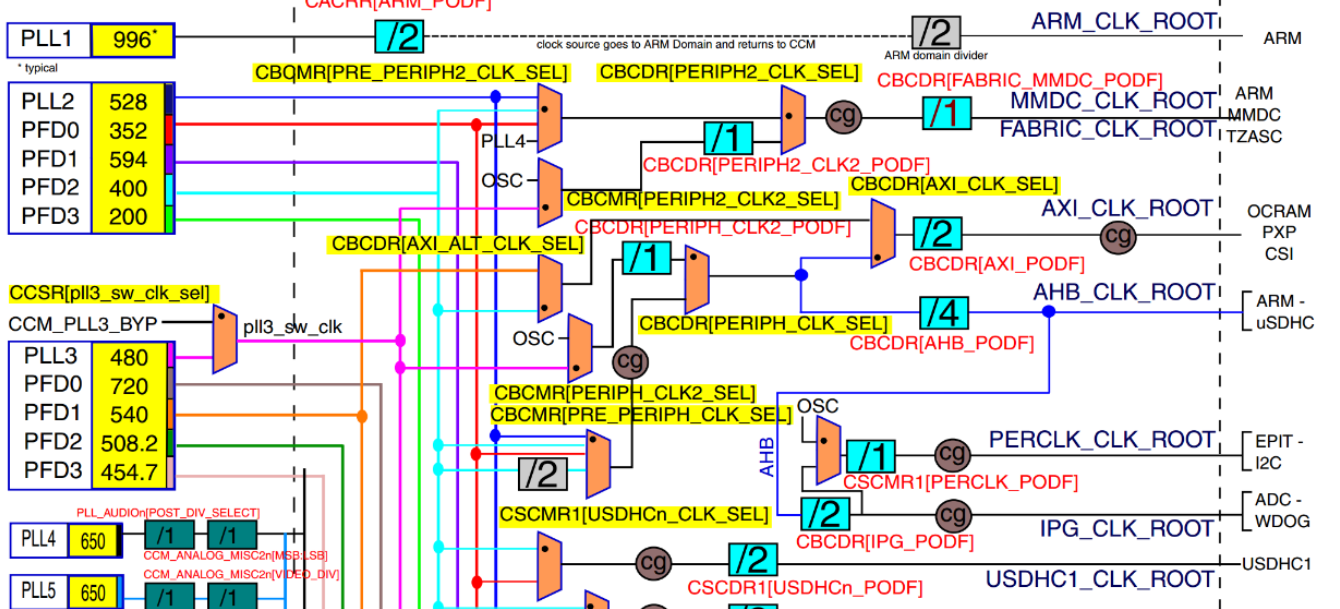

首先是7路PLL, 为了方便生成时钟, 从24MHz生成的, 有的再次生成PFD

时钟树: PLL==>PFD==>外设

- PLL1(ARMPLL): 650MHz-1.3GHz, 提供给ARM内核的

- PLL2(System PLL, 528PLL): 528MHz, 这个是固定的, 分出四路PFD, PLL2_PFD0-3

- PLL3(USB1_PLL, 480PLL): 只要用于USB但是也会用于其他, 固定为480MHz, 也有四路PFD, PLL3_PFD0-3

- PLL4(Audio PLL): 主供音频使用

- PLL5(Video PLL): 主供视频外设, RGB LCD以及图形处理的外设

- PLL6(ENET PLL): 网络连接外设

- PLL7(USB2_PLL): 480Mhz没有PFD

要初始化的PLL以及PFD

PLL1

PLL2以及各路PFD3

PLL3以及PFD

一般按照时钟树里面的值进行设置, 表18-4给出系统时钟的值

配置

主频

PLL1通过CACRR[ARM_PODF]的0-3位控制1-8分频

设置主频为528Mhz, 设置为二分频, PLL1 为1056Mhz, 设置CACRR[ARM_PODF]等于一的时候

设置PLL1

18-5-1-5-1图片

-

PLL1=pll1_sw_clk, 有两路可以选择, 分别为pll1_main_clk 和 step_clk(来自osc_clk等), 通过CCSR[pll1_sw_clk_sel](bit2)进行选择, 为0的时候选择pll1_main_clk,

-

在修改PLL1的时候需要有一个临时的时钟, 在修改的时候切换到step_clk, 有两个来源, 有CCSR[ step_sel](bit8)来进行设置, 0的时候设置为晶振24Mhz

-

时钟切换成功以后就可以修改PLL1的值了

$PLL output frequency = Fref * DIV_SEL/2$

Fref就是晶振, DIVsEL就是CCM_ANALOG_PLL_ARM[DIV_SELECT](bit0-6)设置的

设置为528主频的时候, 这个位就是88, 还要设置CCM_ANALOG_PLL_ARM[ENABLE](bit13)位为1

==注:==再切换回来之前一定要设置为二分频CACRR[ARM_PODF]为1

其他PLL初始化

PLL2和PLL3, 他们的频率固定, 528和480, 但是PFD需要初始化

PLL2

寄存器CCM_ANALOG_PFD528用于设置四路PFD的时钟

$PFD0= 528*18/PFD0_FRAC$

PFD0_FRAC is in the range 12-35,占用6位,还有两位其他设置不修改, 其他的四路公式一样

PFD0 = 352M, PFD1 = 594M, PFD2 = 396M, PFD3 = 297M

PLL3设置类似

设置其他外设时钟源配置

这里初始化PERCLK_CLK_ROOT, IPG_CLK_ROOT, USDHC1_CLK_ROOT, 应为之后学习常用, 因为从时钟树得知PERCLK_CLK_ROOT, IPG_CLK_ROOT来自AHB_CLK_ROOT, 所以初始化AHB_CLK_ROOT最大为132M, PERCLK_CLK_ROOT, IPG_CLK_ROOT为66M

图片629页

设置CBCMR[PRE_PERIPH_CLK_SEL](bit18-19)设置为1, 设置使用来源为PFD2不分频, 396M

CBCDR[PERIPH_CLK_SEL](bit25): 外设主时钟, 设置为0走下边

CBCDR[AHB_PODF](bit12-10)三分频, 设置为2, 设置完以后等待完成, 有可能会产生错误, 可以保持默认值

后面差不多了